(An Autonomous Institution)

COIMBATORE-641 035, TAMIL NADU

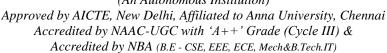

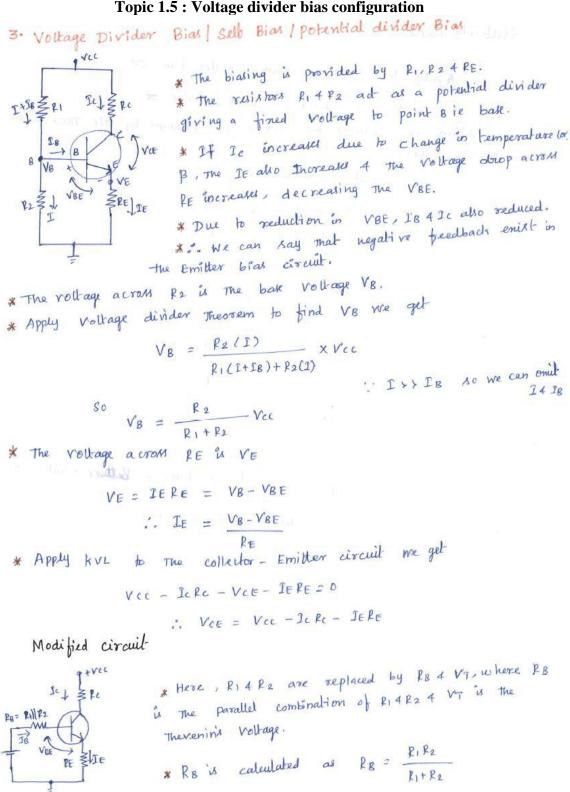

Theri nen's egal circuit

(An Autonomous Institution)

COIMBATORE-641 035, TAMIL NADU

Apply KVL to The Bak-Emiller junction

$$V_T = IBRB + VBE + IERE$$

$$= IBRB + VBE + IERE$$

$$= IBRB + VBE + ICRE + IBRE$$

$$V_T = IB(RB+RE) + VBE + ICRE$$

$$V_T = IB(RB+RE) + VBE + ICRE$$

$$V_T = IB(RB+RE) - ICRE$$

Stability Factors

S

# Here The Therinen's Voltage  $V_T$  is given by

$$V_T = \frac{P_0 \ V_{CC}}{R_1 + R_2} + R_1 \ R_2 \ replaced by R_8.$$

\* Apply KVL to The bak-Emilter junction

$$V_T = IBRB + VBE + (IB+IC)RE - 0$$

\* Alignmentiate eqn 0 w·r· to IC 4 VBE to be independent of IC

We get

$$0 = \frac{\partial IB}{\partial IC} R_B + 0 + \frac{\partial IB}{\partial IC} R_E + \frac{\partial IC}{\partial IC} R_E$$

$$0 = \frac{\partial IB}{\partial IC} (R_B + R_E) + R_E$$

$$\frac{\partial IB}{\partial IC} = \frac{-R_E}{R_B + R_E}$$

\* W·K·T

$$S = \frac{1+\beta}{1-\beta(\frac{\partial IB}{\partial IC})} = \frac{1+\beta}{1-\beta(\frac{-R_E}{R_B + R_E})}$$

\* Take ICM

$$S = \frac{(1+\beta)(R_S + R_E)}{R_S + R_E + R_E} = \frac{(1+\beta)(I_S + R_E)}{R_S + R_E + R_E}$$

\* Dividing each term by  $R_E$  we get

$$S = \frac{(1+\beta)(R_S + R_E)}{R_B + (H_B)R_E} = \frac{(1+\beta)(I_S + R_E)}{R_B + (H_B)R_E}$$

\* Dividing each term by  $R_E$  we get

$$S = \frac{(1+\beta)(R_S + R_E)}{R_B + (H_B)R_E} = \frac{(1+\beta)(I_S + R_E)}{R_B + (H_B)R_E}$$

\*  $R_B + (H_B)R_E$

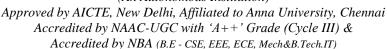

(An Autonomous Institution)

COIMBATORE-641 035, TAMIL NADU

\*The ratio

$$R_{B}|_{PE}$$

controls value of stability factor S. \*If  $R_{B}|_{PE}$  221 Than  $S = \frac{|H|_{P}}{|H|_{P}} = 1$

S' =  $\frac{\partial J_{C}}{\partial V_{BE}} |_{JCO4|_{P}}$  compact

\* With T

$I_{C} = I_{I} + \beta_{I} I_{ICO} + \beta_{I} B_{I} \longrightarrow 0$

$V_{BE} = V_{T} - (R_{E} + R_{E}) I_{B} - R_{E} I_{C} \longrightarrow 0$

\* By rewriting The equity of interms of  $I_{B}$

$I_{B} = \frac{I_{C} - (H_{B}) I_{CO}}{P}$

\* Substitute  $I_{B}$  in equity  $I_{B}$  we get

8  $V_{BE} = V_{T} - (R_{E} + R_{B}) I_{B} - R_{E} I_{C}$

$= V_{T} - (R_{E} + R_{B}) I_{B} - R_{E} I_{C}$

$= V_{T} - (R_{E} + R_{B}) I_{B} - R_{E} I_{C}$

$= V_{T} - (R_{E} + R_{B}) I_{B} - R_{E} I_{C}$

\* Take The common terms  $I_{E} I_{C} + (I_{E} + I_{B}) I_{CO} - I_{E} I_{C}$

\* Take The common terms  $I_{E} I_{C} + (I_{E} + I_{B}) I_{CO} - I_{E} I_{C}$

\* Take  $I_{C} I_{C} = I_{C} I_{$

(An Autonomous Institution)

Accredited by NBA (B.E - CSE, EEE, ECE, Mech&B.Tech.IT) COIMBATORE-641 035, TAMIL NADU

VBE =

$$V_T - (R_B + (I+B)R_E)I_C + [(R_E + R_B)(I+B)]I_D$$

=  $V_T - [R_B + (I+B)R_E]I_C + V' - D$

\* We can rewrite The eqn © interms of  $I_C$

$$[R_B + (I+B)R_E]I_C + V_T - V_BE$$

$$ge = \frac{(V_T - V' - V_{BE})^{\beta}}{(V_T - V' - V_{BE})^{\beta}} - ge = \frac{u}{v} \text{ for mat}$$

$$U_S v = \frac{du - u}{v^2} dv$$

\* differentiating eqn (7) w. r. to B

$$\frac{\partial I_L}{\partial \beta} = \frac{RB + (I+\beta)RE(V_T - V' - V_BE) - \beta(V_T - V' - V_BE)RE}{(RB + (I+\beta)RE)^2}$$

\* Multiply numerator 4 denominator by (1+B) 1 B

$$= \frac{(1+\beta)(RB+RE)(VT-V'-VBE)\beta}{\beta(1+\beta)(RB+RE(1+\beta))(RB+RE(1+\beta))}$$

$$= \frac{S}{\beta(1+\beta)}$$

$$= \frac{S}{\beta(1+\beta)}$$

$$= \frac{S}{\beta(1+\beta)}$$

$$= \frac{S}{\beta(1+\beta)}$$

$$S'' = \frac{I_c S}{\beta(1+\beta)}$$

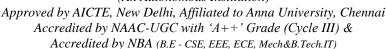

Advantages

\* The Stability factor S for voltage divider bias is less as compared to another biasing circuit \* So This circuit is more stable 4 hence it's most commonly und.

(An Autonomous Institution)

COIMBATORE-641 035, TAMIL NADU

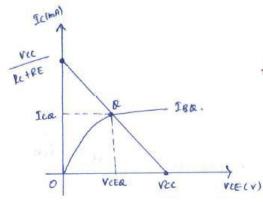

Load line Analysis for vollage divider bias

\* Apply KVL to the collector-Emitter circuit

AM whe IE ~ Ic

\* This equation represents the de load line with slope of - 1 44 interrupt

\* When Ic =0 is the transistor is in cut-off region

\* When VCE = 0 is The transistor is in saturation region

\* Thus The 2 end points are (vec. 0) 4 (0, rec ) By joining Thek & end points , a De lord line is drawn.

\* The saturation current for the circuit

's

$$T_{e,sal} = \frac{V_{c,c}}{P_{c,c} + P_{E}}$$