#### SNS COLLEGE OF TECHNOLOGY

#### Coimbatore-35 An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A++'(III Cycle) Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

23ECB201- DIGITAL SYSTEM DESIGN

II YEAR/ III SEMESTER

UNIT 1 - BOOLEAN THEOREMS AND LOGIC REDUCTION

Topic - Implementation Using Universal Gates

### **NAND** and **NOR** implementation

- > Any Boolean function can be created using AND OR and NOT gates.

- >AND, OR and NOT gates can be implemented using NAND and NOR gates.

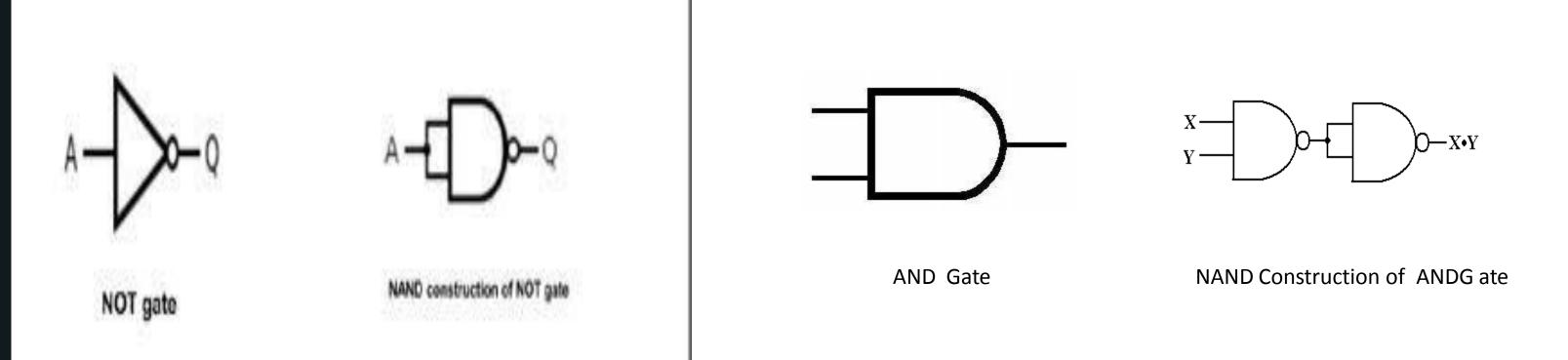

# NAND implementation - Implementation of NOT and AND using NAND gate

- A NAND gate with single input acts like a NOT gate.

- As a NAND gate is the invert of AND so by putting an inverter on the output of NAND we can have AND gate.

### **Symbolic Equivalence of NAND Gate**

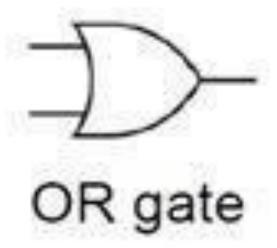

# NOR implementation - Implementation of OR gate using NOR gate

➤ As NOR is the invert of OR gate so by putting an inverter in the output of NOR we get OR gate

NOR implementation of OR gate

13-Sep-24

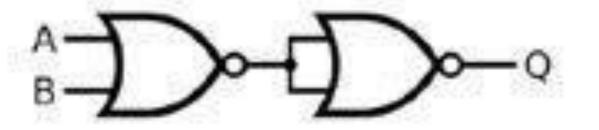

### **Graphical equivalence of NOR gate**

> By De Morgan's Law we can describe NOR gate graphically by the following symbols

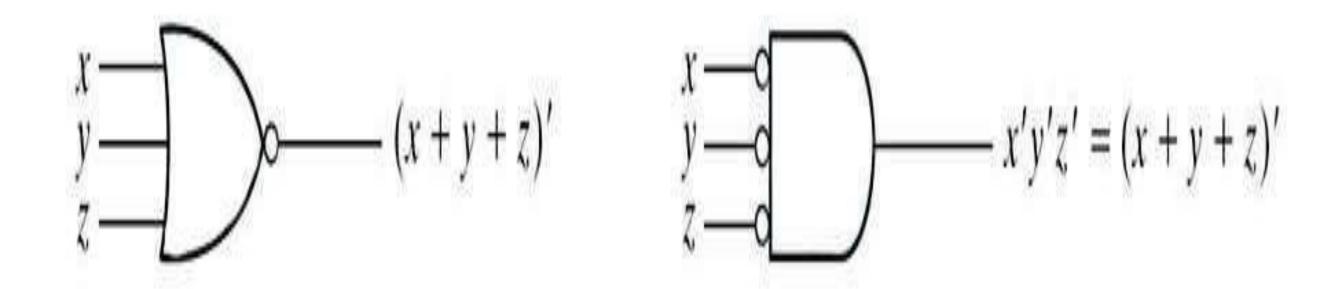

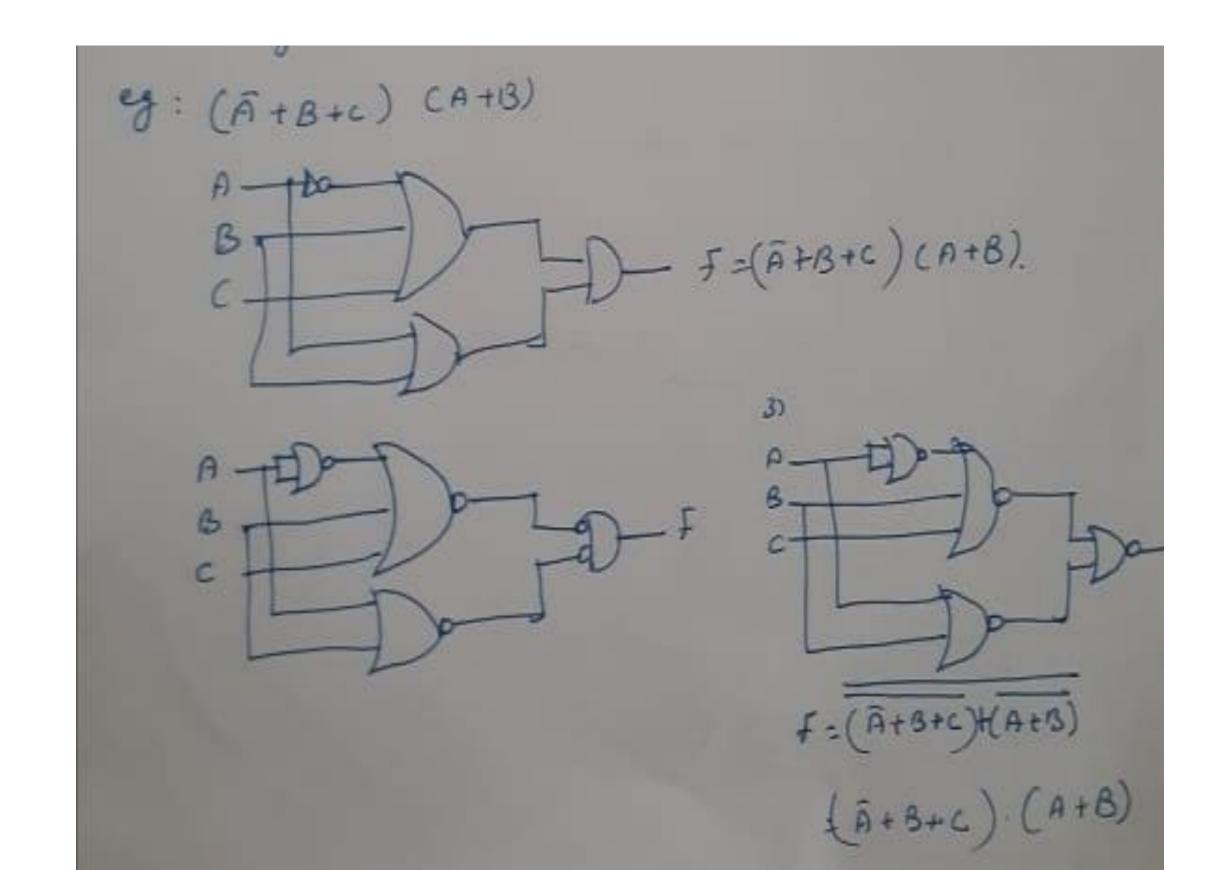

NAND-NOR Implementation!

NAND - NAND Implementation; (According to DR mayon's theorem)

$$\frac{A}{S} = \frac{1}{A} + B + C$$

procedure !-

- (i) simplify the given logical expression and convert of in the sop form

- (ii) Draw the AND-OR-NOT realization

- (15) Replace every And gase by a MAND I every OR gate by a bubbled OR gete & NOT gete by a NAND inventor

- (ii) finally draw the circuit using only NAND gates

Lyample

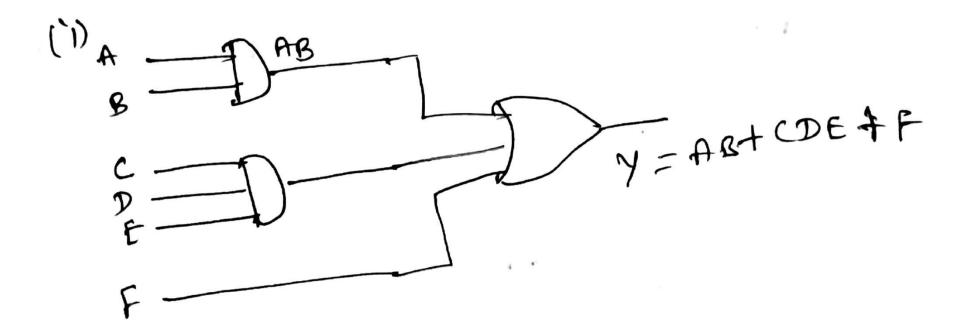

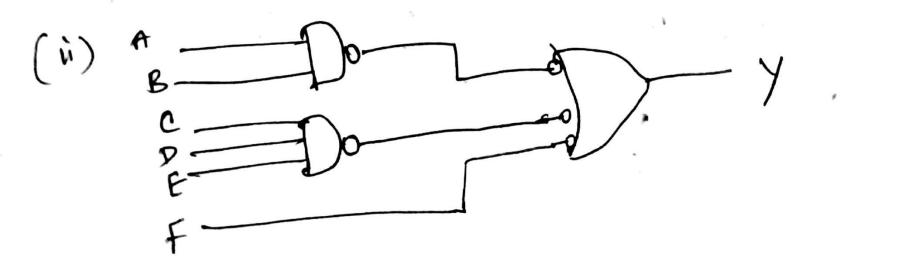

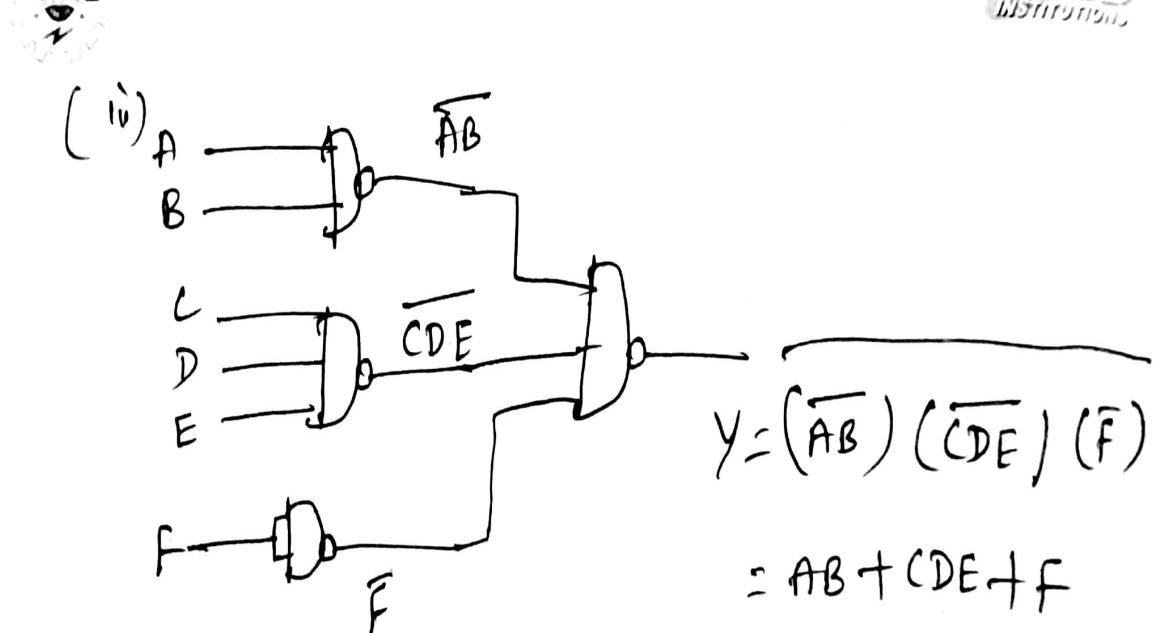

Implement the following Boolean function wing only getter . Y = AB + CDE + F

NAND gates

(i) expression convert it into por form

- (ii) draw AND-OR-NOT redization

- (iii) Replace every OR gate by NOR, AND by a bubbled AND

(iv) Replace every OR gate by NOR, AND by a bubbled AND

gate and inverter by a NOR invertey

(iv) Finally, draw the final circuit by only the NOR gate.

### **THANK YOU**